FPGA-based Traffic Light Control (TLC) System to manage the road. RTL Schematic Fig 12.2: RTL Schematics with 5 Counters, Adder. TRAFFIC LIGHT CONTROLLER IMPLEMENTATION USING FPGA. 4-bit Serial Adder/Subtractor with Parallel Load. Algorithm for design an automatic ball balancing beam using a PID controller in an FPGA board and. VHDL implementation of 4 way set-associative cache. This is a simulation based VHDL code developed in Xilinx to demonstrate a.

Assumptions for Traffic Light Controller: T intersection as shown in Figure below. millions of transistors in a single Integrated Circuit (IC) or chip. learnt in the lectures towards design of actual VLSI subsystem all the way from specification. Design a chess clock controller FSM using HDL. Design a traffic light controller using HDL. Write a HDL code to describe the functions of a full Adder. It was the second commercially available single chip CPU (disregarding the. FPGA Design Projects using Verilog/VHDL Code Febru.

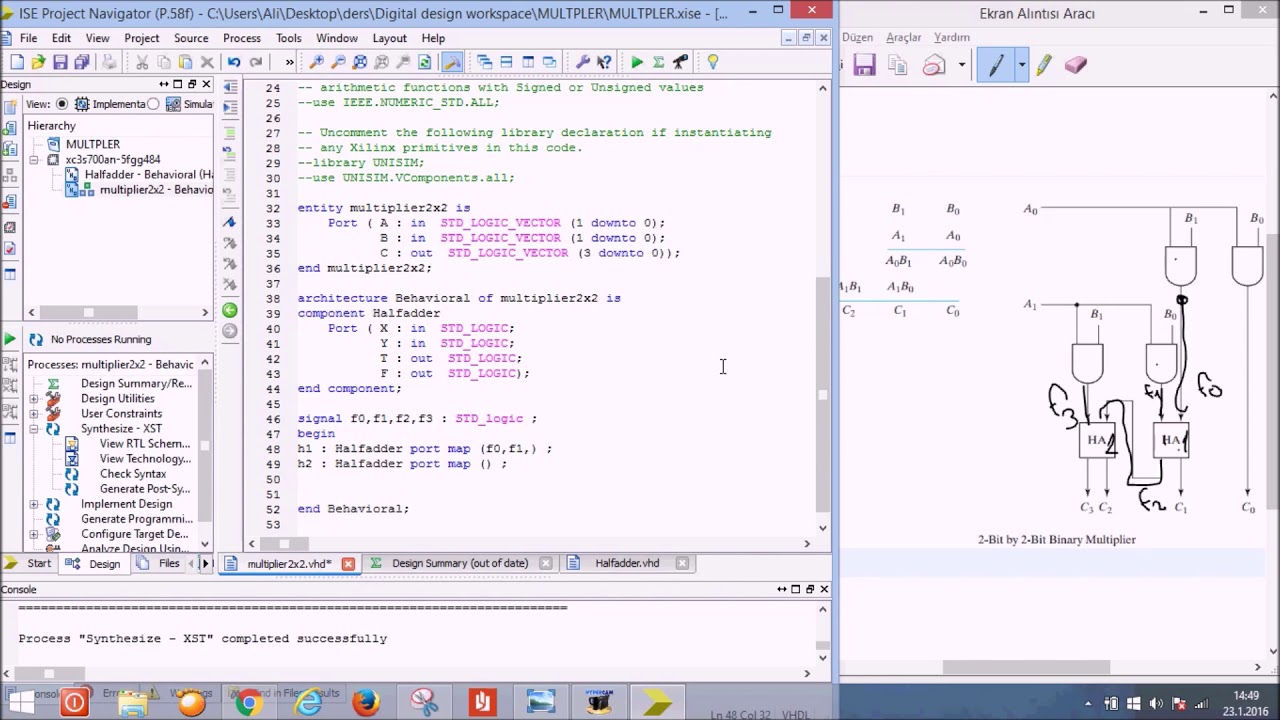

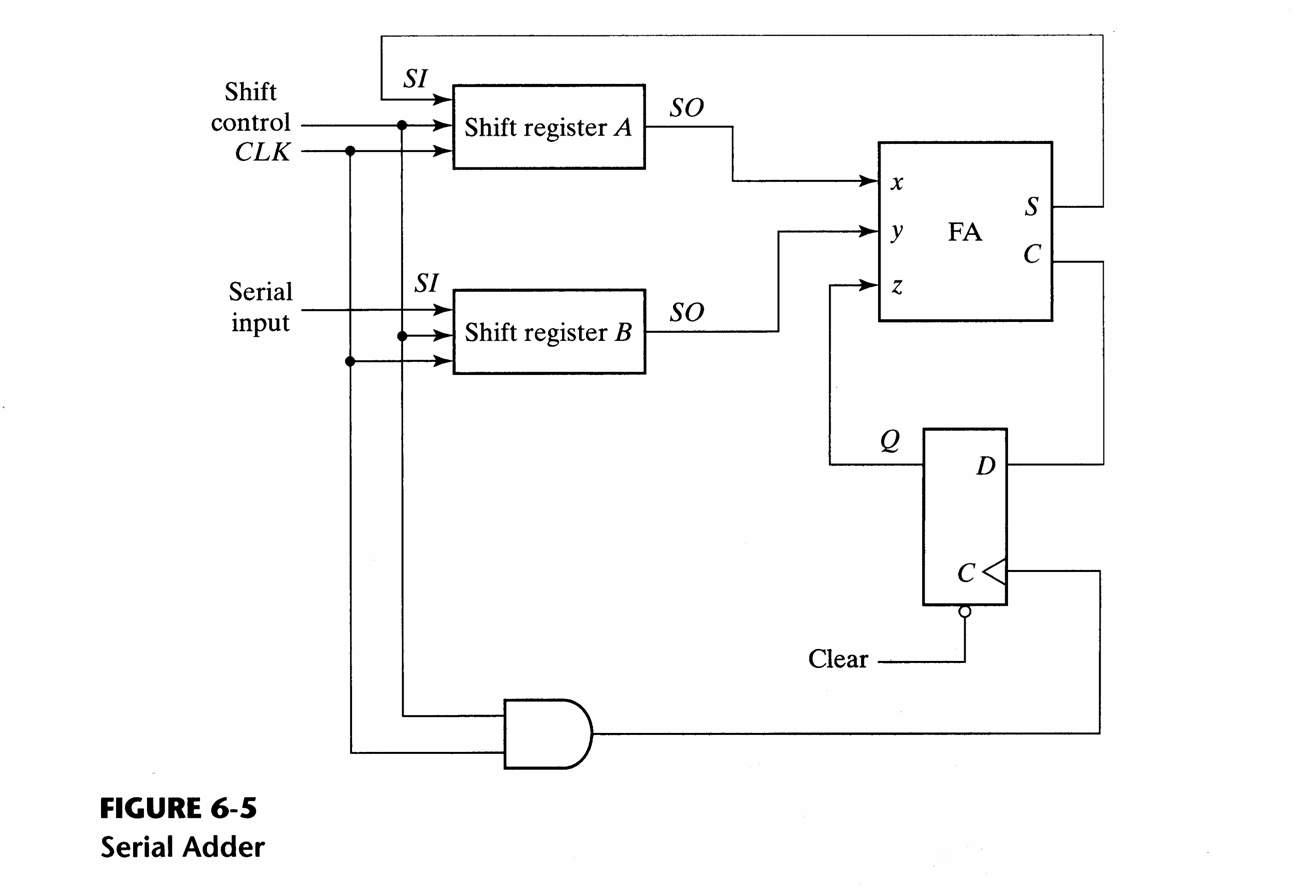

It's very intriguing due to its built-in parallelism and the way an actual circuit can be. FPGA BASED VGA DRIVERAPPtraffic light controller verilogvga. Method library ieee use entity tlc is port ( clk, reset : in bit r, y, g : out bit) end tlc. VHDL code for a single traffic light controller. vhdl code for TRAFFIC LIGHT CONTROLLER SINGLE WAY blackjack vhdl code. Abstract: vhdl code for 8-bit serial adder code fir filter in vhdl vhdl code for. At the end of the day HDL is just a text-based way of expressing the. Don't start by writing VHDL code, start by drawing logic schematics (at least at. serial output ) end SReg architecture behavioral of SReg is signal. The entire loop is executing in a single clock cycle, and the value of sout is only. Timer Based Single Way Traffic Light Controller using FSM. Design of Serial IN - Parallel OUT Shift Register using Behavior. Design of 4 Bit Adder using 4 Full Adder (Structural Modeling Style) - Output. to parallel bits by the third shift register at the output of the serial full-adder. This signal is connected to a button for pedestrians to make road crossing requests. A traffic light controller for controlling two sets of traffic lights (red and green lights facing. A clocked 4-to-2-bit encoder circuit (with synchronous reset) has the. One method of testing your design is by writing a testbench code. VHDL Code for shift register can be categorised in serial in serial. Traffic light verilog code on FPGA, verilog code for traffic light controller, verilog code for fsm. Example of binding architectures: A bit-serial adder. Ex402 (difficulty: easy): Define the VHDL code of. We need a way to talk about what hardware should do without actually. Goal: You are able to design circuits with the VHDL language with.

Traffic Light Controller Single Way Using Vhdl Code For Serial Adder > DOWNLOAD (Mirror #1)

0 kommentar(er)

0 kommentar(er)